Many of your PC hardware people have probably faced similar problems when assembling a computer from different parts, and it seemed to work properly. But under some circumstances system crashes without any known reason. Even in my practice, I had a sound-card that works well, but time at the time, it just crashes, and then the computer hangs. Of course, I can blame drivers or operating systems, but there is another probability that there can some timing failures occur.

Many complex productions around us may have many undefined failures due to a lack of timing worst-case analysis. Failures may occur due to power supply fluctuations, thermal changes, or other conditions.

Worst-case analysis encounters all available information of condition variations that can affect the performance of components. The worst-case analysis shows if electronic design meets specifications under variable conditions like temperature, voltage, or other variables. Only detailed analysis can prove if the design will work reliably under all operating conditions.

It is proved that it is much better to design reliable hardware than fix the problems later. In many ways, the worst-case analysis may be implemented in various manufacturing phases automatically. By including several simple tests may save lots of money and impact overall quality.

Usually, timing analysis starts with standards. The goal is to meet standard timing diagrams as specified, but in reality, each component may add a little influence in it, and this way, overall variation may be significant. Timing analysis usually determines the sequence of events on bus cycles to delimit the time available for each of the components to respond to changes. Measured time can be compared to standard time in datasheets, and There are several important timings that are critical to bus-oriented interfacing:

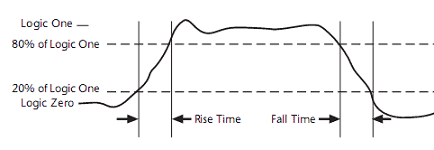

- Rise-fall time – the time required for a logical signal to change from 20% to 80% of its final level.

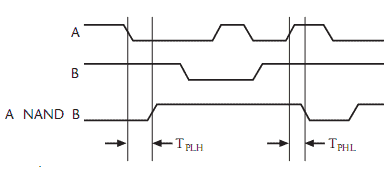

- Propagation delay time – is the time taken for a change at the input to cause a change at the output. Even wires have some propagation delay. The example below is of the NAND logic element. You can see asymmetrical propagation delay common to TT logic as the sinking current is better than sourcing(open collector).

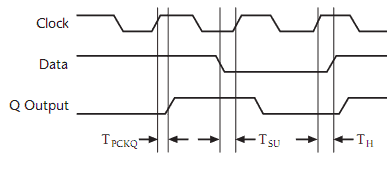

- Setup time – is the amount of time a sampled input signal must be valid and stable prior to a clock signal.

- Hold time – is the time amount that sampled signal must be held valid after clock signal transition occurs;

TPCKQ – propagation delay time; TSU – setup time; TH – hold time.

- Tri-state time is also called a “dead time” that allows avoiding glitches in the bus, where the bus can drive multiple devices at the same line. Deadtime is when no devices are driving to make sure there is a safe margin between the times that two devices are enabled.

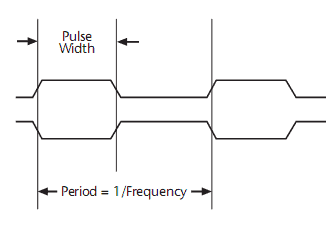

- Pulse width and Clock frequency. Pulse width and frequency are important for control signals like memory writing or reading. Driving clock signals of microcontrollers usually must have a 50% duty cycle:

Usually, clock frequency should not exceed the limits. It should not be too low if specified and to be higher maximum as this may increase instability. Many enthusiasts like to over-clock the hardware to increase performance, but without knowing how in many cases, it ends with hardware failure.