This is an important part of understanding ARM operation modes and handling them. ARM7 supports seven types (0x00000014 address is reserved) of exceptions:

As you can see in the table, each exception has its own name and fixed address, so-called exception vectors. When an exception occurs, execution is forced from a fixed memory address corresponding to the type of exception. When an exception occurs, R14 and SPSR registers act like this:

R14_<mode>=return link(PC+4);

SPSR_<mode>=CPSR;

CPSR[4:0]=exception mode number;

//execute in ARM state

CPSR[5]=0;

//disable fast interrupts

if (<mode>==reset or FIQ) CPSR[6]=1;

//disable normal interrupts

CPSR[7]=1

PC=mode vector address

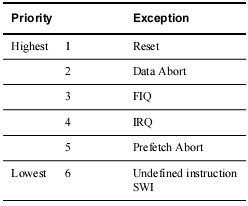

Each exception has priorities. Table below shows how priorities are assigned to exceptions:

Note. All chip peripherals are served as FIQ and IRQ. More deeply about exceptions and priorities will be in practical examples later.