ARM7 architecture has a normal 32bit ARM7 instruction set and a compressed 16-bit instruction set, the so-called “Thumb.” ARM7 instructions have complex behavior. As ARM processor programming is usually written in C, there is no need to be an ARM expert, but understanding the basics may help develop efficient programs.

ARM7 datatypes

ARM7 processor can support following datatypes:

- 8 bit signed and unsigned bytes;

- 16 bit signed and unsigned half-words;

- 32 bit signed and unsigned words

But shorter than 32-bit data types are supported only by data transfer functions, but when internally processed, they are extended to 32-bit size. ARM7 core doesn’t support floating point datatypes – they can only be interpreted by software.

ARM memory organization

ARM7 is capable of storing words in two ways, depending on whether a significant byte is stored. If the word MSB is stored at the highest byte, then the operation is called “little-endian” if MSB is stored at the lowest position, then it is called “big-endian.”

Usually, it is easier to work with little-endian people as they expect to be LSB at the lowest position. Endian is selected in compiler settings.

ARM conditional instructions

Comparing to other RISC microcontrollers, almost all ARM7 core instructions are conditionally executed. As conditional branches are standard instructions, ARM instructions were extended by adding 4 bit at the top of the 32-bit instruction field:

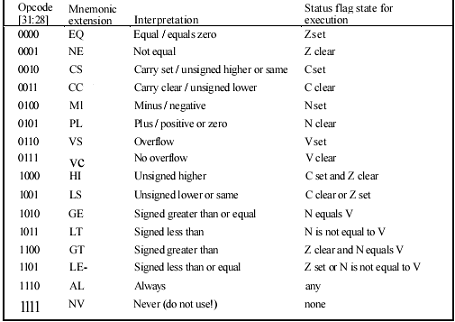

As the condition field has 4 bits, there can be 16 condition values. According to the condition – instruction can be executed or skipped. As we know, conditions depend on N, Z, C, and V flags in the CPSR register. Available conditions:

Don’t use ‘NV’ as it will act as a ‘nop’ operation. But it is reserved and may change in other ARM platforms. The behavior of this is not guaranteed.

Conditional instructions are one factor that keeps a smooth program flow through the pipeline. As we know, when the usual branch occurs, the pipeline is flushed and starts refiling from the beginning.

Practically speaking

if(x<100) {

x++;}

would compile in most efficient ASM code using one conditional command.

ARM7 instruction groups

ARM7 instructions split in six main categories:

- Branching;

- Data processing;

- Data transfer;

- Block transfer;

- Multiply;

- Software interrupt.

Branching allows jumping forwards and backwards up to 32MB.

There are two main types of branching:

- Branch jump with/without link exchange (link exchange means that current PC value is stored in R14 link register);

- Branching with/without link exchange and instruction set exchange between ARM<->Thumb(The only recommended instruction to swap between ARM and Thumb).

Data processing includes all Logical, adding/subtracting, testing instructions (conditional/unconditional) like AND, EOR, SUB, RSB, ADD, ADC, SBC, RSC, TST, TEQ, CMP, CMN, ORR, MOV< BIC, MVN.

For instance, compiler C code: if(z==1) R1=R2+(R3x4) should compile optimally to like

EQADDS R1, R2, R3, LSL #2

Data transfer instructions are used to move signed/unsigned Word, half-Word, and Byte data to and from the selected register. LDR and STR mnemonics.

Block transfer instructions are used to copy multiple registers with a single instruction. Using LDM and STM instructions, it is possible to Load and Store the whole register bank or subset.

Multiply instructions are used to multiply operations. There are two subsets of operands MUL, MLA for 32bit results and MULL, MLAL for 64-bit results.

Software interrupts instruction SWI transfers execution to address in memory location 0x00000008 and changes the mode to svc. SWI instruction can also be conditional. SWI instruction has 24 unused bits that can be used for storing data or custom code, which can be decoded in svc mode. This feature is handy in embedded OS when making operating system calls. Software interrupt will be discussed in other articles.

Wery good Reference of ARM Instructions can be downloaded from here: armref